#### Hewlett Packard Enterprise

# Ultra-energy-efficient integrated DWDM optical interconnects for future HPC systems

Ray Beausoleil, John Bowers, Stanley Cheung, Antoine Descos, Mario Dumont, Yingtao Hu, Zhihong Huang, <u>Geza Kurczveil</u>, <u>Sri Priya Sundararajan</u>, Bassem Tossoun, Yating Wan, Xian Xiao, Yuan Yuan

Hewlett Packard Labs geza.kurczveil@hpe.com

UC Santa Barbara mariodumont@ucsb.edu

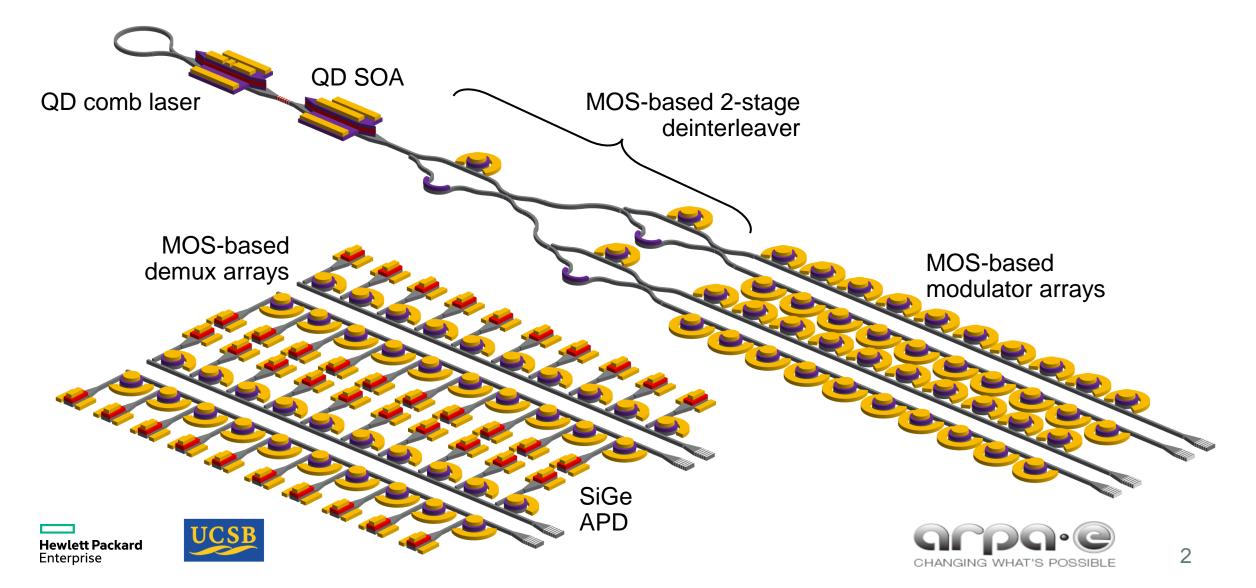

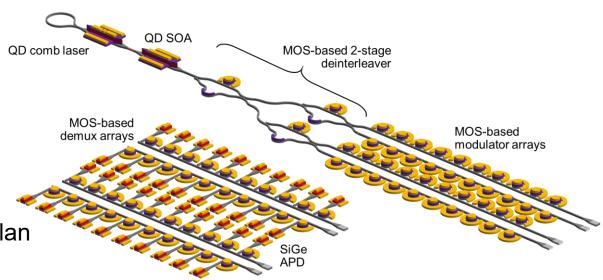

# Program Goal: >1 Tb/s, <1.5 pJ/b\* link with FEC-free BER ≤ 10<sup>-9</sup> at 50°C \*Laser, SOA, modulator, tuning of optical components, APDs

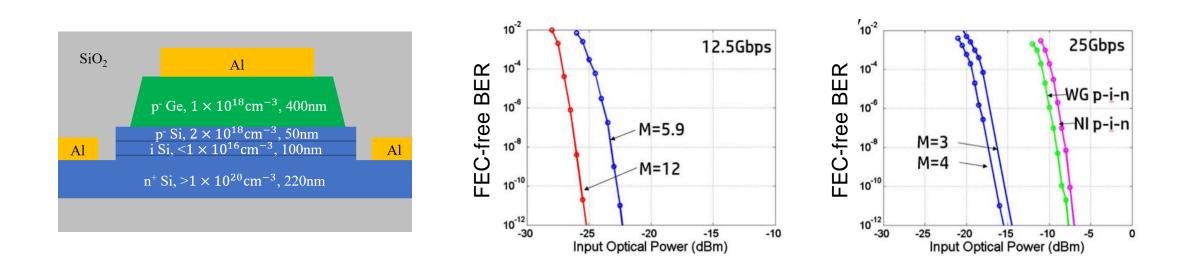

#### SiGe APDs

- Gain in photodetector  $\rightarrow$  better sensitivity  $\rightarrow$  can drive laser at lower drive current  $\rightarrow$  energy savings

3

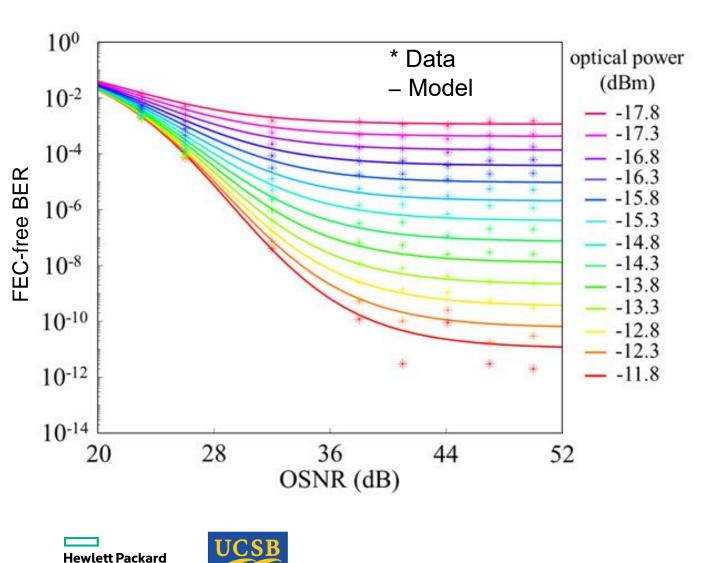

#### SiGe APDs

Enterprise

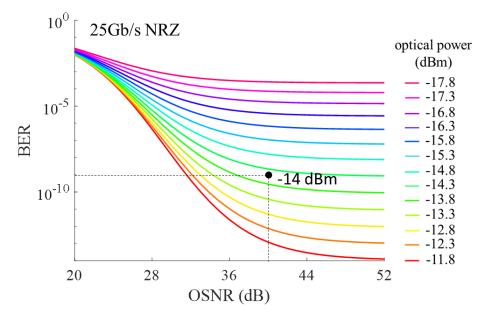

- Need OSNR  $\geq$  36 dB for FEC-free BER  $\leq$  10<sup>-9</sup>

- HPC favors FEC-free BER ≤ 10<sup>-12</sup> because of latency

#### **Comb laser**

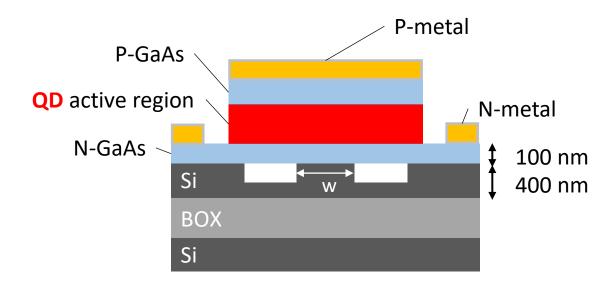

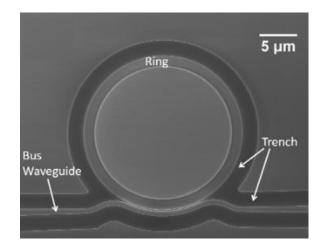

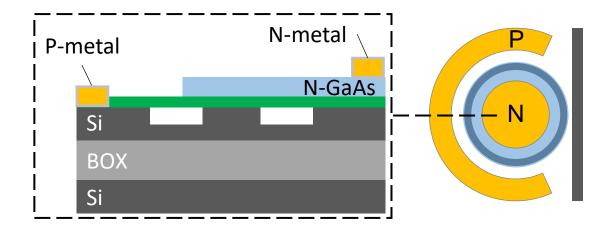

- -Bond GaAs-based QD material to SOI

- Design layer thicknesses for efficient coupling between Si and III-V

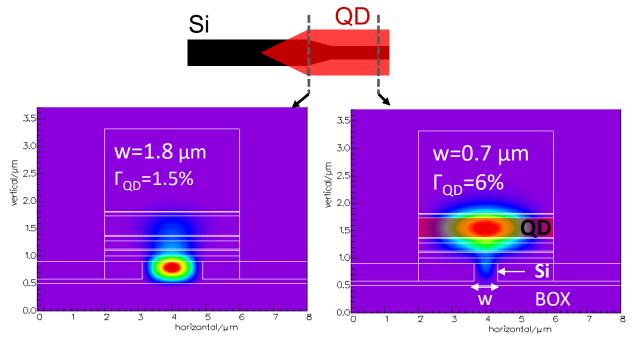

- Adjust QD confinement through Si waveguide width

#### **Comb laser design**

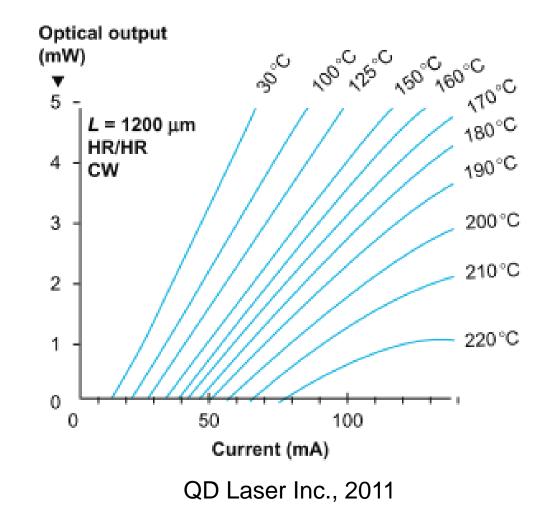

- SOI: 400 nm Si (SOITEC)

- QD: 5 QD layers (QD Laser, Inc.)

- $W_{mesa} = 6 \ \mu m$

- W<sub>Si</sub> = 475 nm

- $\Gamma_{dot}$  ~4% ( $\Gamma_{dot+barrier}$  ~35%)

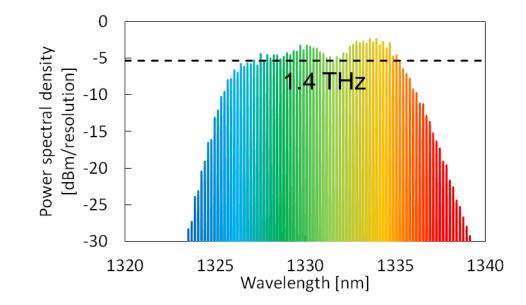

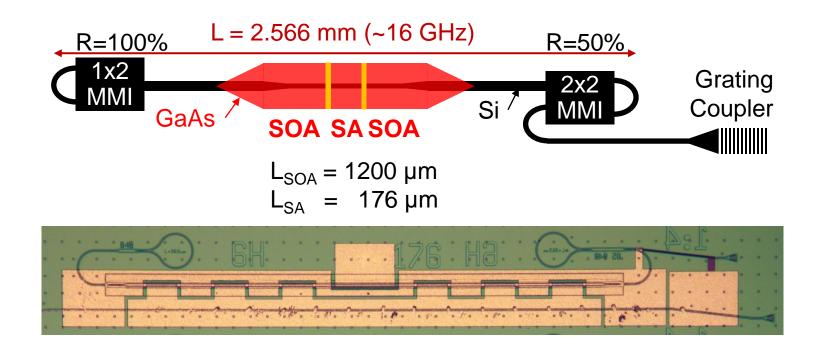

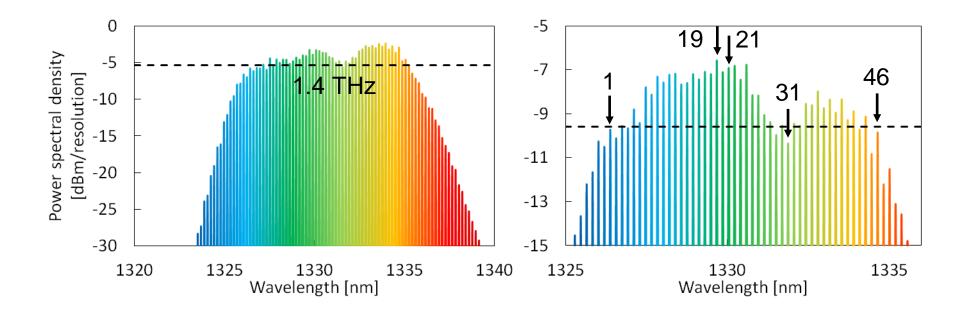

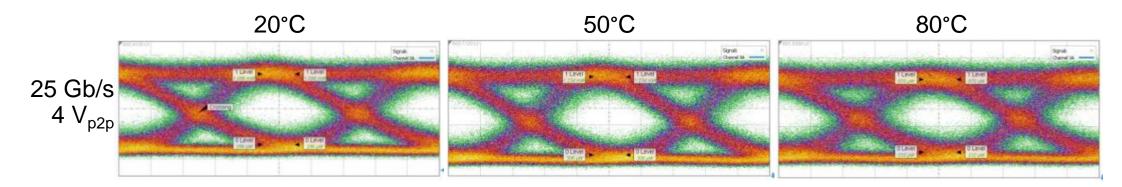

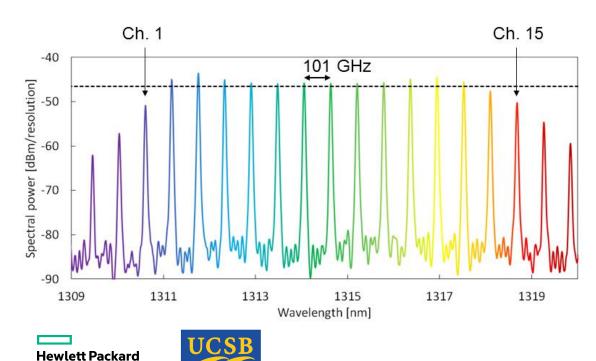

#### Comb laser data @ 50°C, continuous wave

- Comb laser: 260 mA, 1.96 V  $\rightarrow$  509 mW, SA = -6 V

- Channel spacing defined by lithography

### Comb laser data @ 50°C, continuous wave, !external! modulation

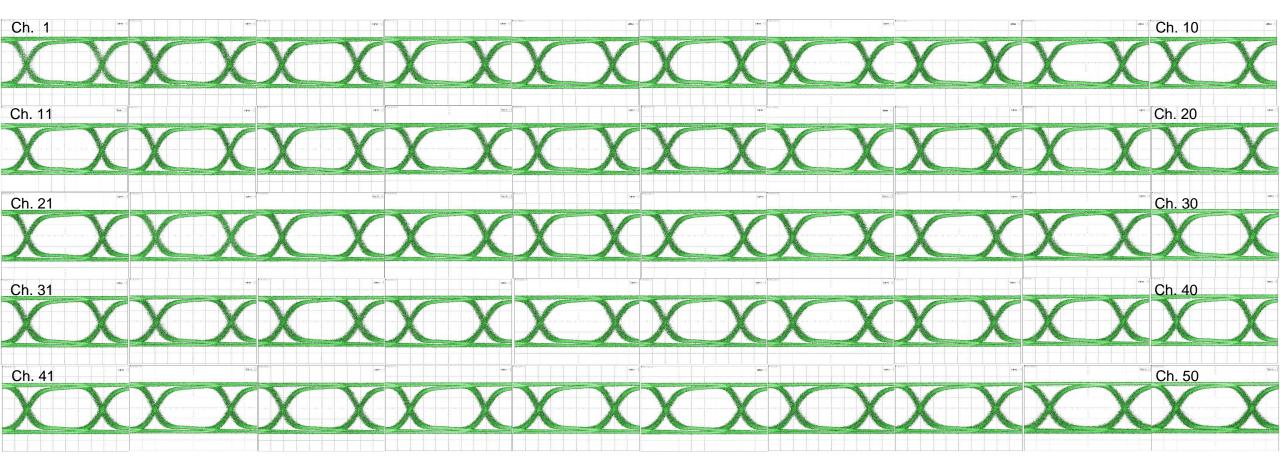

50 comb lines @ 10 Gb/s (setup limited) = 500 Gb/s with 509 mW laser power @ 50°C

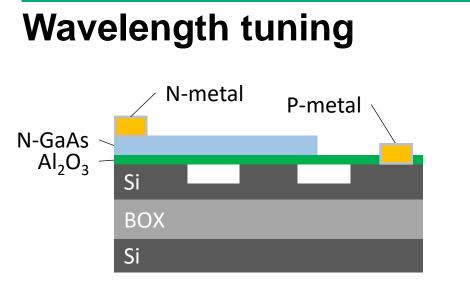

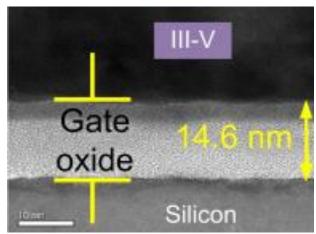

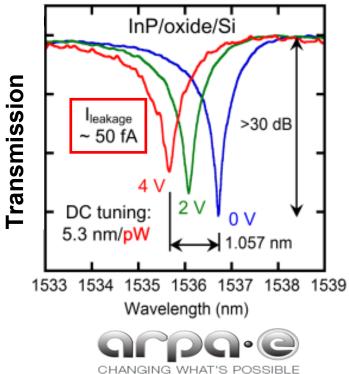

- Bonding oxide between III-V and Si forms inherent capacitor

- DC voltage  $\rightarrow$  carrier accumulation  $\rightarrow$  refractive index change  $\rightarrow$  resonance shift

- No current flow  $\rightarrow$  negligible power consumption

Hewlett Packard Enterprise

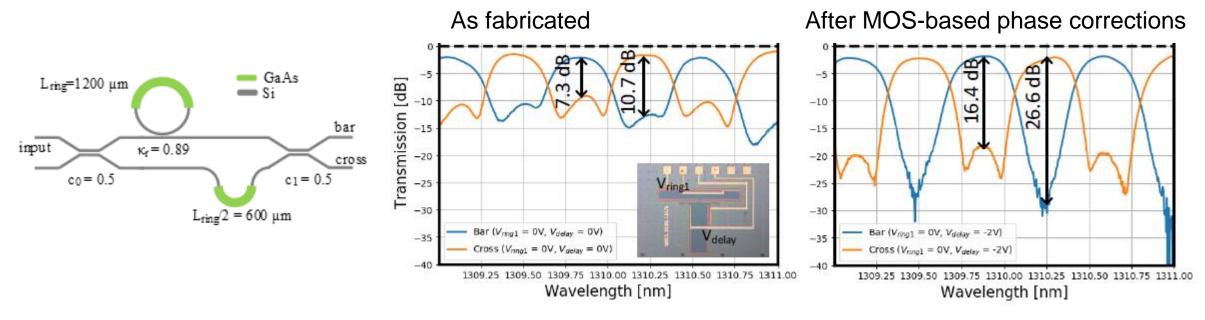

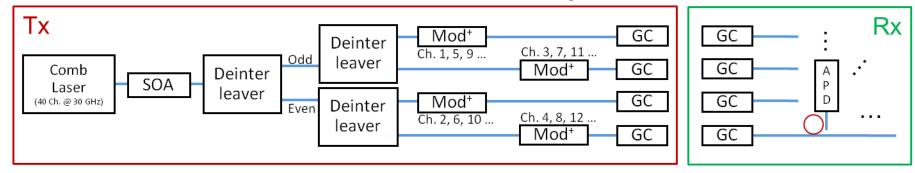

#### **Deinterleavers**

- Comb laser prefers small channel spacing (~30 GHz): wide comb

- Modulator prefers large channel spacing (~120 GHz): low insertion loss and crosstalk

- → Deinterleave 30 GHz comb into four spatial channels @ 120 GHz

2 V, 5 nA  $\rightarrow$  10 nW

#### **MOS Modulator**

#### **Demonstrated so far**

All individual components (laser, deinterleaver, modulator, SiGe APD\*) except for low loss grating couplers

\*SiGe APDs demonstrated in external fab, not integrated with lasers

#### Remains to be done

- Low loss ( $\leq$  3 dB) grating couplers

- Replicate SiGe APD performance in in-house fab

- Integrate everything on one chip

- Tie in design and characterization data to scale up plan

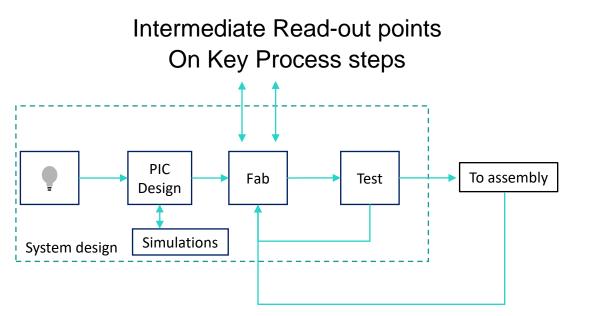

#### Path to Commercialization: Yield Management from Design Phase

- Design phase (MPW/dedicated wafers) facilitate test of multiple design variants- evaluation metrics:

- Key performance targets met? e.g. Data rate, power consumption and BER

- Robustness to process variation? i.e. performance of comb laser repeatably centered in process window

- Designs which perform best to both above criterion chosen to Prototype

- Prototype phase: special builds with detailed failure analysis- sample parts to System Level

- Select best performing design and material system to scale into full volume manufacturing

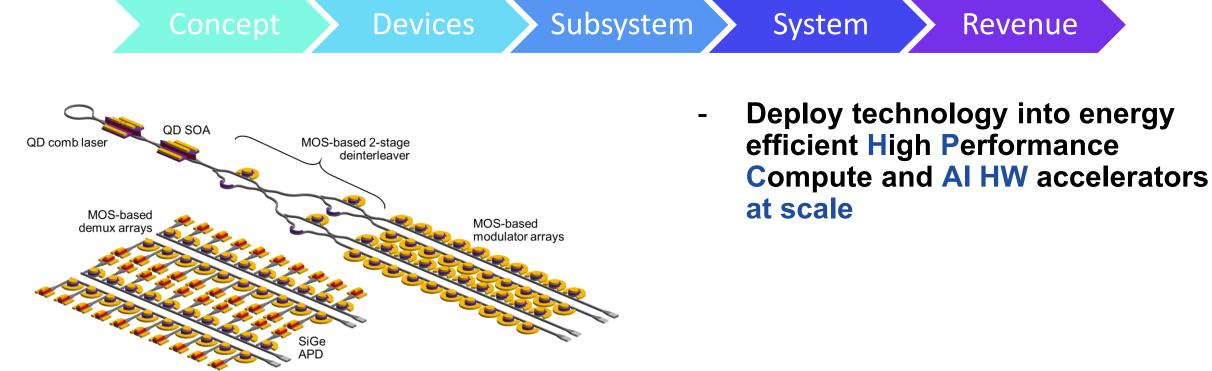

#### Path to Commercialization: Primary Use Cases & Transition Plan

- High Radix switching for High Performance Computing data fabric

- Low power AI Hardware accelerators

| Design<br>Parameter   | Current       | Initial<br>Scaling | Long Term<br>Scaling |

|-----------------------|---------------|--------------------|----------------------|

| # Of<br>channels      | 4 lanes       | 8 lanes            | 16 lanes             |

| Bonded Area/<br>Wafer | 20%           | 60%                | 80%                  |

| Material<br>System    | SOI/GaAs/SiGe | SOI/GaAs/SiGe      | SOI/GaAs/InP/SiGe    |

#### Path to Commercialization: Partners

Use test and assembly data to tune Fab process to Optimal position

- Ecosystem partners identified in US and Europe

- Engagement model and scaling objectives under discussion

- Model is to engage early in product lifecycle, design phase through packaging and test with close yield monitoring

- Transparent data flow with traceability end to end key to successful scaling

#### Summary: Technology and Path to Scale

Following individual components to demonstrate >1 Tb/s, <1.5 pJ/b\* link have been fabricated and characterized: Laser, deinterleaver, modulator and SiGe APD\*

## Backup

#### Transceiver chip energy efficiency goals

<sup>+</sup>One bank of 10 microring modulators

|                 |     |   |                   |            | 863.2 mW |

|-----------------|-----|---|-------------------|------------|----------|

| PD Sens         |     |   | -14.0 dBm         | 1          | 40.0 mW  |

| Demux           | 0.5 | 1 | 0.5 dB            |            |          |

| GC loss         | 3   | 1 | 3.0 dB            |            |          |

| Fiber (10 km)   | 4   | 1 | 4.0 dB            |            |          |

| Passive WG loss | 5   | 1 | 5.0 dB            |            |          |

| GC loss         | 3   | 1 | 3.0 dB            |            |          |

| Modulator       | 0.3 | 1 | 0.3 dB            | 0.58       | 23.2 mW  |

| Deinterleaver   | 0.5 | 2 | 1.0 dB            |            |          |

| Amplifier       | 15  | 1 | 15.0 dB           |            | 300.0 mW |

| Comb laser      |     |   | -12.2 dBm/channel |            | 500.0 mW |

| 50°C            |     |   |                   | Single ch. | N=40     |

25 1000 Gb/s

0.86 pJ/bit

## **Comb laser requirements**

- -Wide gain bandwidth

- -Operation at high temperature

- -Low amplitude noise in <u>**!EACH!</u>** comb line</u>

#### $\rightarrow$ Quantum dot lasers ...

- Integration with high quality passives

Gratings, splitters, rings, ...

- -High yield, volume foundry

- On 300 mm wafers

- $\rightarrow$  ... on silicon

Don't just use Si as a carrier. Take advantage of its excellent passive devices as well!

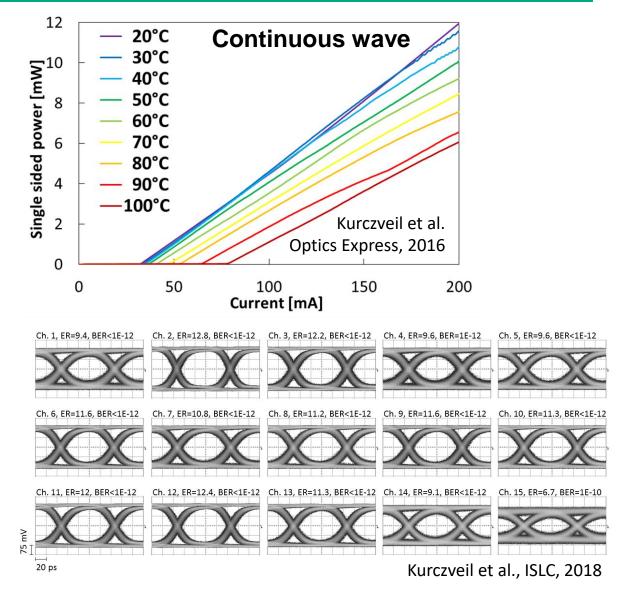

#### **Previous results**

Enterprise

- -100°C operation (CW)

- -3 dB bandwidth: ~6 nm, 12 channels

- -FEC-free BER  $\leq 10^{-12}$  in 14 channels (10 Gb/s, NRZ) @ 20°C

CHANGING

20

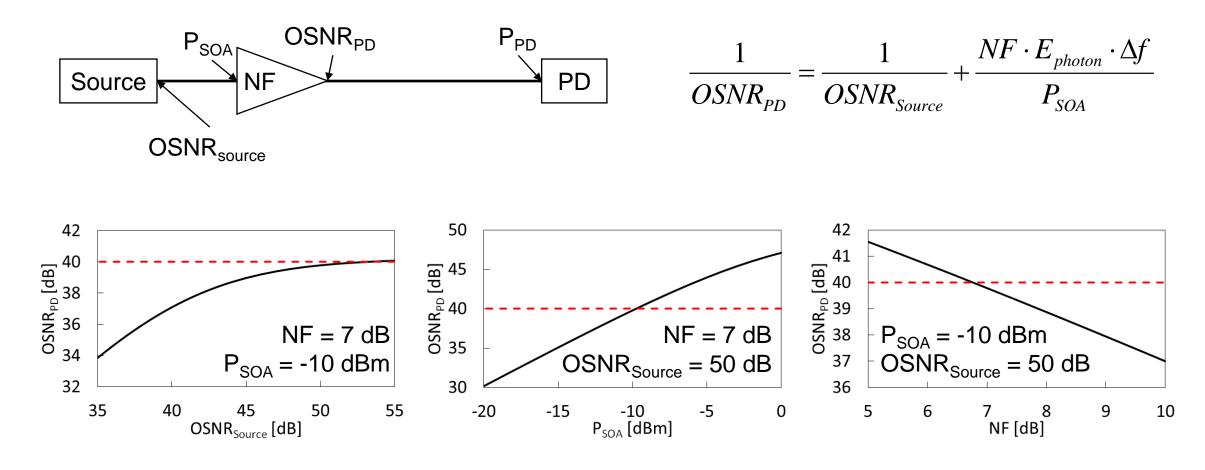

**OSNR**

#### $\uparrow$ OSNR by:

- $\uparrow P_{SOA} \rightarrow$  Place SOA right after comb laser

- $\downarrow$  NF of SOA

21